快报道

光刻工艺套刻设备,本土亟待突破

来源:半导体行业观察

作者:编辑部

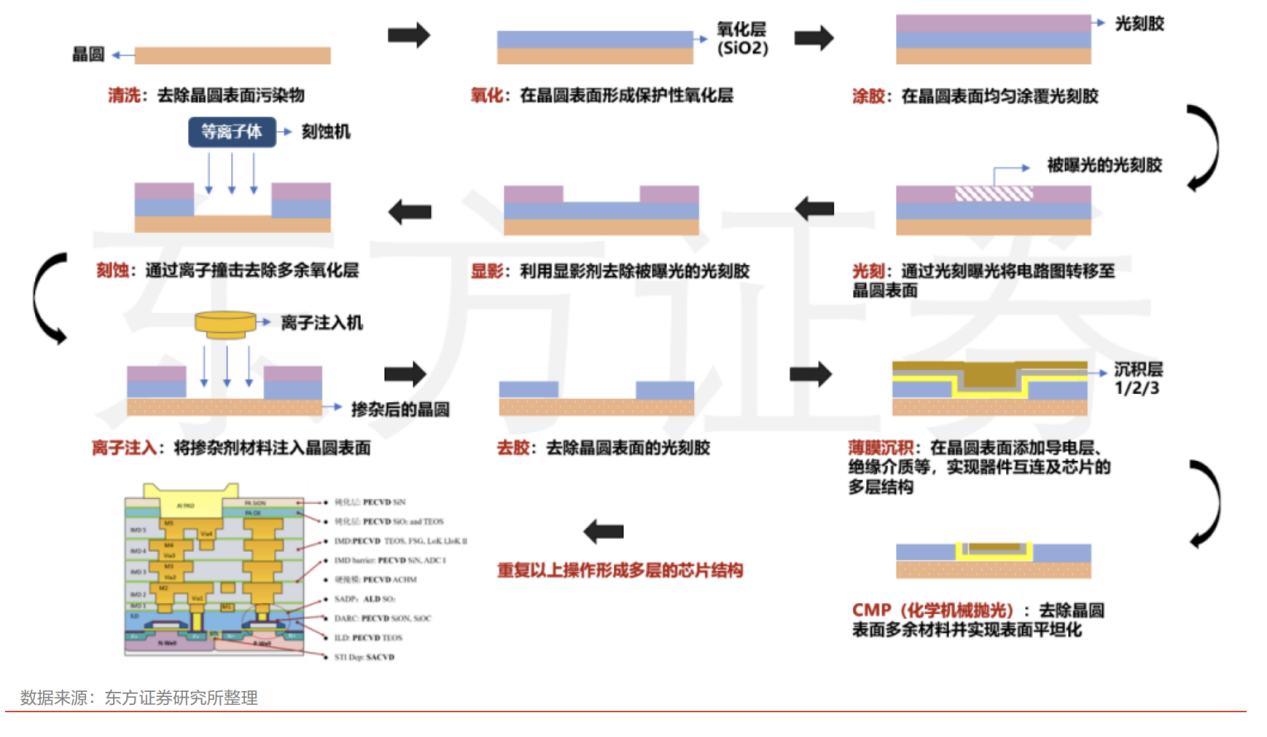

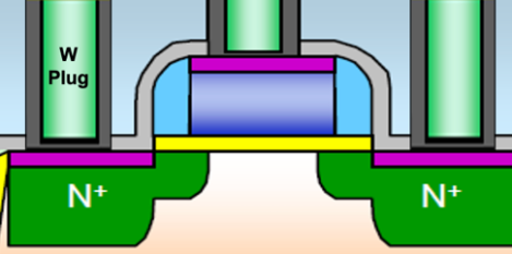

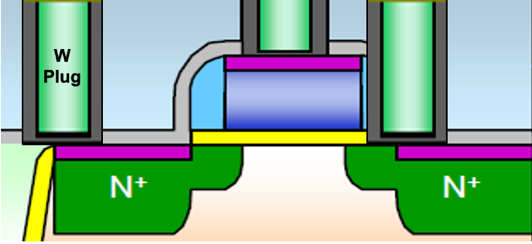

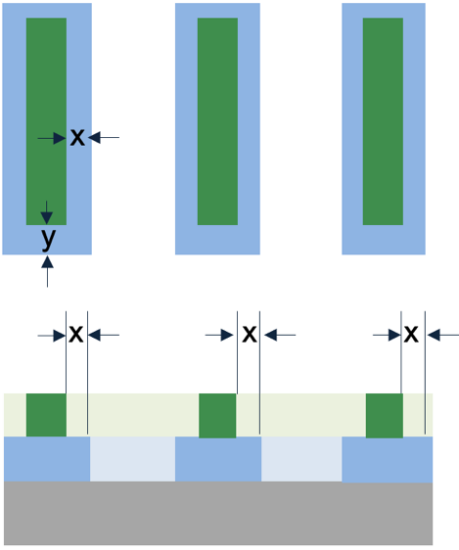

晶圆制造是一个复杂的多层结构构建的过程,每一层平面图形通常先由光刻(涂胶、曝光、显影)工艺定义,再通过刻蚀、薄膜沉积、离子注入、平坦化等工艺构建出三维立体结构。在这个过程中,确保每层图形都被制作在预定位置至关重要。任何不当的偏移,都可能导致晶体管形状不当、金属互联层错位乃至器件失效,从而影响芯片的功能与良率。例如,如果在完成晶体管制造后,用于连接它们的金属孔洞(如钨塞孔)发生了偏移,就会导致器件性能下降甚至完全失效。Overlay设备的任务,就是测量并修正这种层与层之间的“套刻误差”。

符合工艺规定的钨塞孔洞

偏移过度的钨塞孔洞

- 光刻机本身:包括曝光图形的畸变和运动平台的微小误差。

- 其他工艺环节:如刻蚀、薄膜沉积和退火等,这些工艺可能导致晶圆翘曲,间接影响后续光刻的套刻精度。

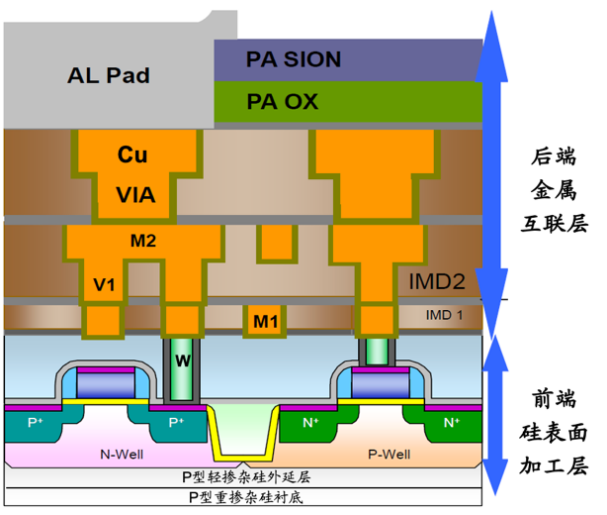

晶圆实际结构示意图(横切面)

- 28nm逻辑电路的关键层套刻误差要求在6nm以内;

- 进入14nm以下制程后,这一比例会变得更小。14nm节点最初要求单次曝光的套刻误差为6.4nm,而双重曝光之间的误差则需达到5.6nm。而14nm经过不断的改进,到了2015年,其关键光刻层的套刻误差要小于5nm[1];

- 7nm制程的关键层套刻误差要求已降至3nm以内;

- 5nm和3nm等更先进的制程,关键层的套刻误差更是需要控制在2.5nm和2nm以内。

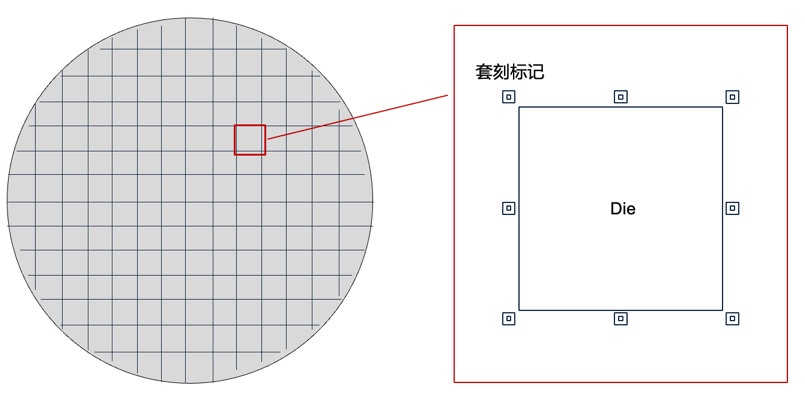

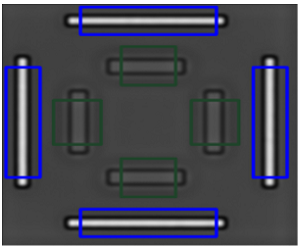

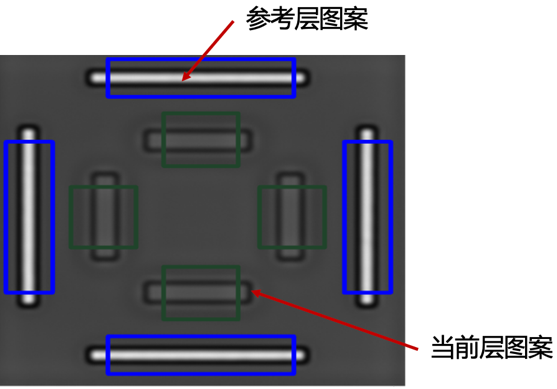

更具体来说,主要通过测量晶圆上预留的特殊“套刻标识图案”来计算误差。这些套刻标识图案通常位于每个Die图案的边或顶点上,前一层(或称之为参考层)的套刻标识图案会随着光刻、刻蚀等工艺保留在晶圆上。而进入当前层工艺之后,新的套刻标识图案在显影之后,会以光刻胶图案的形式出现在当前层。通过获取参考层和当前层的套刻标识图案信息,就可以计算出套刻误差。

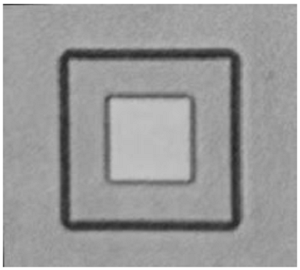

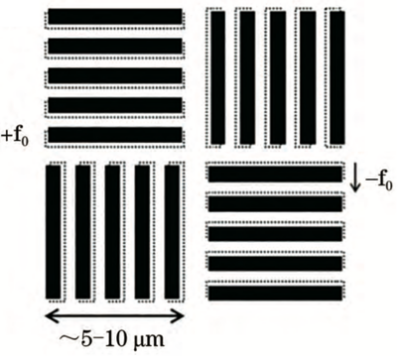

IBO技术采用的套刻标识图案常见的有:(1)盒式套叠型标识Box-in-Box mark,(2)套叠的线条标识Bar-in-Bar mark,(3)先进图像计量型标识Advanced-Image-Metrology(AIM)mark等。如下图所示:

(1)

Box-in-Box mark

(2)

Bar-in-Bar mark

(3)

AIM mark

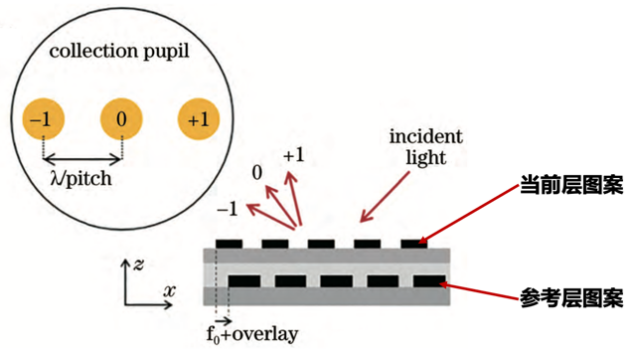

典型的 SCOL 套刻

标记示意图

包含叠加光栅结构的

横截面图

这种需求增长直接体现在设备的配置上:28nm逻辑产线每万片产能通常配备约3台Overlay设备;14nm等先进制程则通常需要3-4台;更先进的工艺对Overlay设备的需求密度持续攀升。同时考虑到先进制程军备竞赛式的扩产,因此,超过80%的Overlay设备需求都来自先进制程工艺。

KLA是套刻测量设备较早的参与者,其设备性能经历了20年以上的考验,并参与了套刻测量标准的制定,是传统意义上的套刻设备垄断型企业,目前占据了60-70%的市场份额。KLA的技术路径以IBO路径为主,目前较新的Archer 800机型已经支持5nm及以下制程的关键膜层。除了IBO之外,KLA在DBO技术路径上开发了ATL系列,主要支持7nm以下的工艺节点。据估算,KLA的套刻设备大约占据其全球收入的8-10%,按照KLA近两年全球收入约100-120亿美元计算,套刻设备每年为KLA贡献了10亿美金的收入体量。

比较两家的竞争优势,理论上,DBO技术路径能支持的极限分辨率比IBO技术路径更高,而且ASML DBO方案所采用的套刻标记图案面积较小,未来具备in die标记的潜力,因此未来的发展前景受到重视。但是从实际的使用来看,KLA的IBO设备在存储芯片制造工艺上的稳定性更好,而ASML凭借其在光刻机光学、算法和运动平台方面积累的经验,在逻辑芯片制造工艺上的分辨率和测量速度具备优势。对于DBO方案,KLA的ATL系列和ASML的Yieldstar系列在国际头部晶圆厂的竞争较为激烈。目前各个Fab对于IBO和DBO技术路径的选择尚无定论。

在中国大陆晶圆厂对于IBO和DBO的使用层面,由于大陆最主要的晶圆厂制程还是在14nm及以上的节点,同时考虑到晶圆厂的良率标准和工程师的使用习惯,因此当前大陆晶圆厂绝大多数选用的技术路径还是以IBO(即KLA的Archer系列)为主,仅个别7nm及以下的晶圆厂会考虑使用DBO。

短期内,KLA和ASML两大巨头的Overlay地位难以撼动。这是因为Overlay设备的技术门槛极高,集“光、机、电、磁、软件、算法、微环境”于一体,性能要求苛刻,技术壁垒极⾼,是精度要求最⾼的前道量测设备之一。

Overlay设备的性能核心在于精度、速度、一致性、稳定性,仅仅精度和速度两个要求,就使得套刻测量设备的技术难度远超一般的光学量测设备。

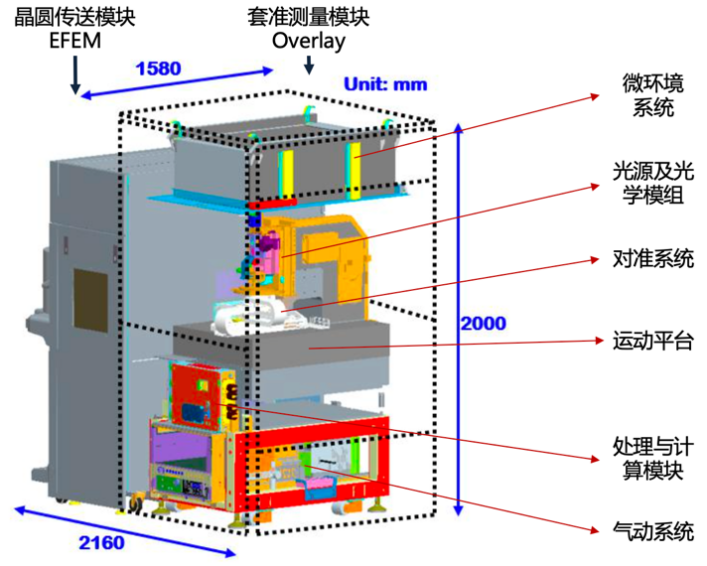

实际上,套刻测量设备的性能绝大部分来自硬件系统的贡献,剩下少部分来自软件和算法。套刻测量设备的硬件系统主要包括:光源及光学模组、对准系统和运动平台(运动台+减震)等。其中,光源及光学模组提供测量必须的光路,确保足够的分辨率,采集原始数据并通过对应算法解析出结果。对准系统负责于测量前,在微米级尺度上快速完成必须的光学和定位准备。运动平台负责实现亚微米级运动控制,包括X-Y-T运动、Z运动等,同时配以减震系统降低环境震动、结构震动、运动晃动带来的干扰,以确保每次将晶圆运送到指定位置。其中,光学模组、对准系统和运动平台的性能要求显著高于一般的CD测量设备,尤其是运动台和减震的稳定性要求。

对于套刻设备(也包括其它量测设备),最大的难点还是设备的一致性(Tool-to-Tool Matching)。简单说就是同一片wafer, 在同一个Fab厂的任何一台套刻设备测量结果要求是一致的,测量结果差异非常小。对于14nm制程,套刻设备一致性的要求已经到0.3nm,这个对于有上千个部件的设备是个极大的考验。然而,这个是套刻设备能够进入量产线一个必要条件。

2020-2024年,大陆晶圆厂在28nm及以上成熟制程的扩产热潮为国产设备提供了市场机遇。“十四五”期间,预计晶圆厂建设投资超万亿元,其中设备投资约8000亿元,28nm及以下制程设备需求占80%以上,Overlay设备需求约90亿元。2025年后,随着人工智能算力芯片驱动的先进制程扩产,Overlay设备的需求密度将进一步提升,为国产厂商带来更大舞台。

自2020年起,一些国内厂商开始进入这个高门槛赛道。虽然在90nm等成熟制程上,国产设备已经能满足基本量产需求,但在更先进的45nm及以下制程上,我们与国际巨头如KLA、ASML在一致性和稳定性层面的差距依然显著。尤其是在28nm及以下先进制程的关键膜层,国产设备还无法实现稳定量产(这里的量产主要指各个制程节点的关键膜层。例如设备进入28nm产线不代表一定可以满足关键膜层的需求,如果仅应用于非关键膜层,则设备实际能满足的CD甚至可能仅为90nm)。

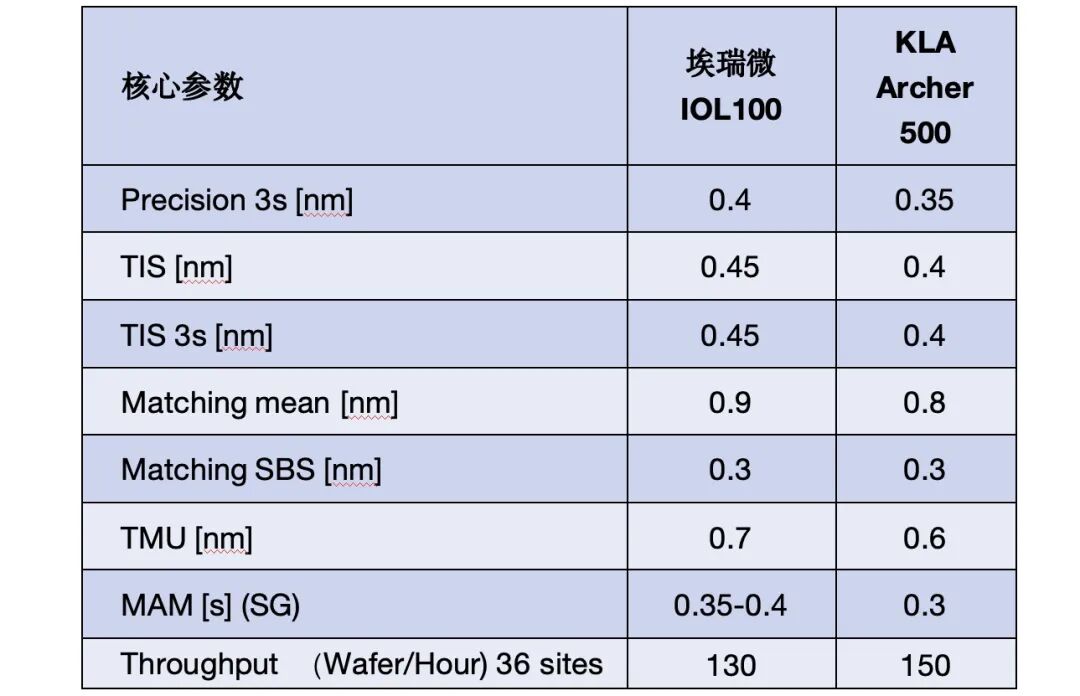

无锡埃瑞微半导体设备便是国产套刻设备赛道中的一颗新星。公司核心团队源于KLA上海研发中心的整建制团队,曾主导Archer 500(针对14nm制程)设备的开发与量产(全球销量200-300台),并参与了Archer 600(10nm)与Archer 700(7nm)的关键设计,服务过台积电、英特尔、三星等顶级晶圆厂。埃瑞微是国内唯一自主掌握原始核心技术(IBO+DBO路径)的团队,具备从零到一、从部件到整机系统的开发能力以及从1到N的大规模设备量产能力。这份“血统”让其在技术上形成断层式领先,许多国内零部件供应商反馈,埃瑞微提出的关键指标是他们首次遇见,且指标要求远超本土竞品。

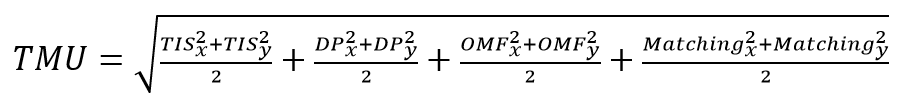

目前埃瑞微已经完成首款对标Archer 500产品的研发,对标Archer 700的产品将于年底进入内部demo 阶段。首款设备面向28~14nm Logic/Memory晶圆厂,采用IBO技术,支持300/200mm晶圆。功能方面,支持BIB/AIM/TripleAIM套刻标识测量;兼容半导体自动化GEM300协议;内置Recipe模板仓库,缩短创建时间,提升机台利用率;实现OVL原始数据在线分析,反馈至光刻设备(KTA功能);支持SG/DG模式。

埃瑞微首款产品参数

其中,零部件的国产化是绕不开的核心难题。套刻设备是一个复杂的系统工程,涉及光学、机械、电子、算法和软件等多个领域。特别是在光学和运动台等关键环节,国内与国际的差距依然明显。

埃瑞微深知,简单的使用国外现成的供应链,没有办法保持可持续发展,并且面临供应链中断的系统风险。因此,他们从成立之初就将目光锁定在零部件的国产化上。他们不再是简单地使用国内现有的供应链,而是主动与国内供应商紧密合作,提供严苛的技术指标和设计指导。通过与供应商的深度绑定,埃瑞微不仅帮助他们克服技术难关,甚至直接参与到零部件的设计与测试中,共同提升国产供应链的整体水平。这种“授人以渔”的合作模式,不仅让埃瑞微的核心零部件实现了完全国产化,更为中国半导体产业链的长期发展铺平了道路。

据悉,埃瑞微将在首款套刻测量设备研发成功的基础上,凭借7nm以下先进制程设备的研发经验,计划在未来两年内实现先进制程套刻设备的量产。

Overlay设备国产替代的道路充满挑战,但趋势不可逆转。唯有 Fab、设备厂与供应链形成合力,才能打破技术垄断。埃瑞微的尝试,或许将成为国产 Overlay 设备突围的重要注脚。